# Diseño y simulación de un demodulador QPSK utilizando Lazo de Costas

## Design and simulation of a QPSK demodulator using Costas Loop

Presentación: xx/10/2024

### Tomas A. De Caso

Grupo SITIC - Dpto. de Ing. Electrónica - Facultad Regional Bahía Blanca - Universidad Tecnológica Nacional - Bahía Blanca - Argentina.

[tomasdecaso0@gmail.com](mailto:tomasdecaso0@gmail.com)

### Juan F. Loidi

Grupo SITIC - Dpto. de Ing. Electrónica - Facultad Regional Bahía Blanca - Universidad Tecnológica Nacional - Bahía Blanca - Argentina.

Servicio de Análisis Operativos, Armas y Guerra Electrónica de la Armada, Punta Alta, Argentina.

[juanfloidi@gmail.com](mailto:juanfloidi@gmail.com)

### Christian L. Galasso

Universidad de la Defensa Nacional – FADARA – ESOA, Punta Alta, Argentina.

Grupo SITIC - Dpto. de Ing. Electrónica - Facultad Regional Bahía Blanca - Universidad Tecnológica Nacional - Bahía Blanca - Argentina.

Servicio de Análisis Operativos, Armas y Guerra Electrónica de la Armada, Punta Alta, Argentina.

[cgalasso@frbb.utn.edu.ar](mailto:cgalasso@frbb.utn.edu.ar)

### Adrián H. Laiuppa

Universidad de la Defensa Nacional – FADARA – ESOA, Punta Alta, Argentina.

Grupo SITIC - Dpto. de Ing. Electrónica - Facultad Regional Bahía Blanca - Universidad Tecnológica Nacional - Bahía Blanca - Argentina.

[alaiuppa@frbb.utn.edu.ar](mailto:alaiuppa@frbb.utn.edu.ar)

### Martin H. Amado

Grupo SITIC - Dpto. de Ing. Electrónica - Facultad Regional Bahía Blanca - Universidad Tecnológica Nacional - Bahía Blanca - Argentina.

[martinamado@frbb.utn.edu.ar](mailto:martinamado@frbb.utn.edu.ar)

### Resumen

En el presente trabajo, se describe el diseño y simulación de un demodulador QPSK, cuyo propósito es integrar un modem de comunicaciones navales. Para ello, se utilizó un circuito de Lazo de Costas para realizar la recuperación de portadora. El demodulador, se simuló en un software matemático y posteriormente en VHDL. Para corroborar el funcionamiento del sistema, se lo simuló con diferentes niveles de ruido.

Palabras clave: QPSK; Demodulador; Lazo de Costas; Simulación; Testbench; SNR; AWGN; FPGA; VHDL.

### Abstract

This work, describes the design and simulation of a QPSK demodulator, intended for integration into a naval communications modem. For this purpose, a Costas loop circuit was used to perform a carrier recovery system.

The demodulator was simulated on a mathematical software and VHDL. To check the system's performance, it was tested with different noise levels.

Keywords: QPSK; Demodulation; Costas Loop; Simulation; Testbench; SNR; AWGN; FPGA; VHDL.

## Introducción

En el presente escrito se aborda el desarrollo y la integración de un demodulador QPSK, para un módem que trabaja con señales en banda de audio de 0 a 3kHz, para comunicaciones en canales de HF y VHF. Para ello, se trabajó el diseño y simulación del mismo tanto en un software matemático como en VHDL.

El modem utilizado actualmente, cuenta con modulaciones tales como FSK y BPSK. Por lo tanto, el demodulador QPSK debe ser capaz de convivir con los demoduladores FSK y BPSK.

Desde el punto de vista matemático, existen muchos tipos de sistemas que permiten demodular una señal QPSK. En este trabajo, se aborda un demodulador, que es capaz de recuperar la información de la portadora sin necesidad de contar con un oscilador local en el receptor, y, además, demodular los datos.

## Desarrollo

### Fundamentos

La modulación QPSK, se caracteriza por tener una señal portadora a la que se le varía la fase. Como se trata de una modulación de 4 símbolos posibles que utilizan dos bits cada uno, la portadora podrá tener 4 fases diferentes:  $45^\circ$ ,  $135^\circ$ ,  $225^\circ$  y  $315^\circ$  (Tomasi, 2003). La portadora seleccionada para modular la señal es de 2500Hz, y la velocidad de transferencia deseada es de 1250 baudios por segundo. La frecuencia de muestreo, por su parte, es de 25kHz.

La modulación QPSK se puede ver como una suma de dos señales BPSK en cuadratura, de manera que se puede expresar como la suma de dos ramas I y Q, desfasadas 90 grados entre ellas y con dos fases posibles cada una. Cuando los datos binarios de cada rama cambian de estado, la fase de cada portadora de salida varía entre dos ángulos que están desfasados  $180^\circ$ , logrando así las 4 fases posibles mencionadas anteriormente.

Para diseñar el demodulador, se tuvo en cuenta que la modulación QPSK es una modulación en fase, y, por lo tanto, se requiere de un circuito de detección de portadora que sea capaz de recuperar la fase de la misma. Es muy importante, ya que, si la fase no está correctamente sincronizada, los datos recuperados serán erróneos. Además, el sistema en cuestión, debe contar con una baja tasa de error.

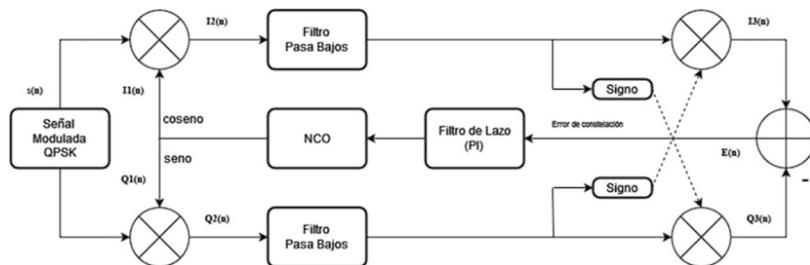

Figura 1: Diagrama en bloques del lazo de costas para QPSK

Las técnicas de demodulación más utilizadas en las señales moduladas en fase se basan principalmente en PLL (phased locked loop) (Campbell, 2016), ya que resultan idóneos para la recuperación y sincronización de la portadora. Como a futuro se necesita implementar el demodulador dentro de una FPGA, el PLL a diseñar debe ser digital (DPLL). Un DPLL (Staszewski & Balsara, MARCH 2005), es un sistema muy utilizado en comunicaciones, y consiste en un sistema de lazo cerrado con la capacidad de sincronizar la fase de un oscilador controlado numéricamente (NCO), en base a la fase de una señal de entrada. El lazo, está integrado por un detector de fase, y un filtro de lazo, que cumple la función de realizar un control PI (proporcional e integral). Luego de realizar una extensa investigación y teniendo en cuenta que el demodulador debe ser

sintetizable en FPGA, se llegó a la conclusión de que el circuito más conveniente para la aplicación en cuestión, es el Lazo de Costas (Osborne, OCTOBER 1982), cuyo diagrama para la implementación en QPSK se muestra en la Figura 1.

Como se puede apreciar, el Lazo de Costas, tiene un diseño similar a un DPLL. El sistema, realiza en primera instancia la multiplicación de la señal de entrada modulada en QPSK, con las señales en cuadratura proveniente del NCO. Luego, mediante los filtros pasa bajos, se eliminan las componentes de doble frecuencia generadas al realizar el producto o mezclado. Dichas componentes, hacen que el sistema requiera una frecuencia de muestreo de al menos 4 veces la frecuencia de la portadora para evitar aliasing.

Luego, se realiza una segunda multiplicación de las señales en cuadratura. La salida de esta multiplicación, corresponde al detector de fase, y será proporcional al error de fase de la señal de entrada con el NCO. Luego, el filtro de lazo realizará un control proporcional e integral del error, que permite sincronizar el NCO con la señal modulada. De esta manera, el Lazo de Costas realiza la recuperación de la portadora y con ello la demodulación QPSK.

A continuación, se realiza el análisis del detector de error de fase. Se supone la presencia de dos señales en cuadratura del NCO con fase inicial  $\phi$  y la siguiente señal de entrada modulada en QPSK:

$$s(n) = A \sin(\omega_c n + \theta) + A \cos(\omega_c n + \theta) \quad (1)$$

La salida de los multiplicadores  $Q_2(n)$  e  $I_2(n)$  (ver Figura 1), es decir, la entrada de cada filtro pasa bajos, será la siguiente:

$$Q_2(n) = (a(t) \cdot \sin(\omega_c n + \theta) + b(t) \cdot \cos(\omega_c n + \theta)) * \sin(\omega_c) \quad (2)$$

$$I_2(n) = (a(t) \cdot \sin(\omega_c n + \theta) + b(t) \cdot \cos(\omega_c n + \theta)) * \cos(\omega_c) \quad (3)$$

A la salida del filtro pasa bajos, se elimina la componente de doble frecuencia generada al realizar el producto. Luego de la sincronización, las salidas de los filtros son utilizadas para demodular los datos  $a(t)$  y  $b(t)$ . Para ajustar la salida del NCO, se utiliza el detector de fase, el cual consiste en tomar el signo de cada rama y realizar un producto cruzado entre ellas, para calcular posteriormente la diferencia entre ellas (error de fase). A la salida del detector de fase, se tiene lo siguiente:

$$E(n) = I_2(n) * \text{sign}(Q_2(n)) - Q_2(n) * \text{sign}(I_2(n)) \quad (4)$$

Para realizar el filtrado, se utiliza un filtro FIR (Finite Impulse Response), el cual es un filtro digital en el que la salida depende de la sumatoria de la entrada actual, y de entradas anteriores multiplicadas por un coeficiente. Se los considera en el demodulador QPSK, porque poseen fase lineal y son sencillos de implementar.

En cuanto al filtro de lazo y el NCO (Ghaffari, Hosseini, & Sadr, 2016), son muy importantes en el lazo de costas. Para el cálculo de los coeficientes  $K_L$  y  $K_I$  del filtro de lazo, se utilizan las ecuaciones (5) y (6).

$$K_L = \frac{2\zeta\omega_n t_s}{K_{NCO}} \quad (5)$$

$$K_I = \frac{t_s \omega_n^2}{K_{NCO}} \quad (6)$$

Donde  $\omega_n$  es la frecuencia natural no amortiguada,  $t_s$  es el periodo de muestreo,  $\zeta$  es el coeficiente de amortiguamiento y  $K_{NCO}$  es la ganancia del NCO.

En cuanto al NCO, el periodo de la señal de salida, es igual al tiempo que le lleva al contador alcanzar su cuenta máxima. De esto último, se desprende que la frecuencia de salida del NCO es:

$$f_o = \frac{f_{clock} * \theta}{2^N} \quad (7)$$

Donde  $f_{clock}$  es la frecuencia de muestreo, N es la resolución de bits del registro de fase y  $\Theta$  es la fase de entrada.

### Simulación de alto nivel

Se desarrolló una simulación matemática del demodulador QPSK siguiendo el diseño del Lazo de Costas detallado anteriormente. El objetivo de la simulación, es el de observar el comportamiento del demodulador, para tener una base teórica y simulada a la hora de realizar el diseño digital en una FPGA.

En primera instancia, se introdujeron los parámetros iniciales del simulador. Se consideraron los siguientes valores: tasa de baudios:  $f_b = 1250 \text{ bps}$ , frecuencia de muestreo:  $f_s = 25 \text{ kHz}$ , Muestras por bit:  $N_b = 20$ , número de muestras:  $N = 40000$  y frecuencia de portadora:  $f_c = 2500 \text{ Hz}$ . Para modular la señal en QPSK, se optó por realizar una suma en cuadratura de dos señales BPSK. Se generó un vector de datos aleatorios, que pasa por un conversor serie-paralelo para separar los bits en dos ramas y así, cada una de ellas, se multiplica por seno y coseno, y posteriormente se suman para realizar la modulación QPSK. Adicionalmente, y para simular un canal de comunicaciones básico y simple, a la señal QPSK generada se le añade ruido blanco gaussiano (AWGN) (Howard, 2015). Esto resulta importante para evaluar el alcance del demodulador, frente a posibles interferencias del canal de comunicaciones. En principio, se genera una señal de 40 dB SNR, prácticamente sin ruido. El paso siguiente, es el cálculo de los coeficientes del filtro de lazo  $K_L$  y  $K_I$ . Para ello, se utilizan las ecuaciones (5) y (6), y con los parámetros utilizados, se obtienen los coeficientes del filtro de lazo. En principio, el coeficiente de amortiguamiento se establece en 0.5. En el caso de la frecuencia natural, se establece en 500 Hz. Estos parámetros, se establecieron de tal forma que la respuesta sea lo suficientemente estable y rápida al mismo tiempo. Posteriormente, se realizó el filtrado de orden 8, con frecuencia de corte en 600 Hz utilizando una función del software, y se calculó el error de fase como se explicó anteriormente. El error de fase, es tomado por el filtro de lazo para realizar el control proporcional e integral, teniendo en cuenta los coeficientes  $K_L$  y  $K_I$ , y el resultado, es guardado en un buffer que luego es realimentado al acumulador de fase. Por otro lado, de cada salida de las ramas, se decide si se establece en 0 lógico o en 1 lógico, dependiendo si la magnitud de las mismas es mayor o menor a cero. Finalmente, las salidas pasan por un conversor paralelo-serie, para obtener los datos demodulados correctamente.

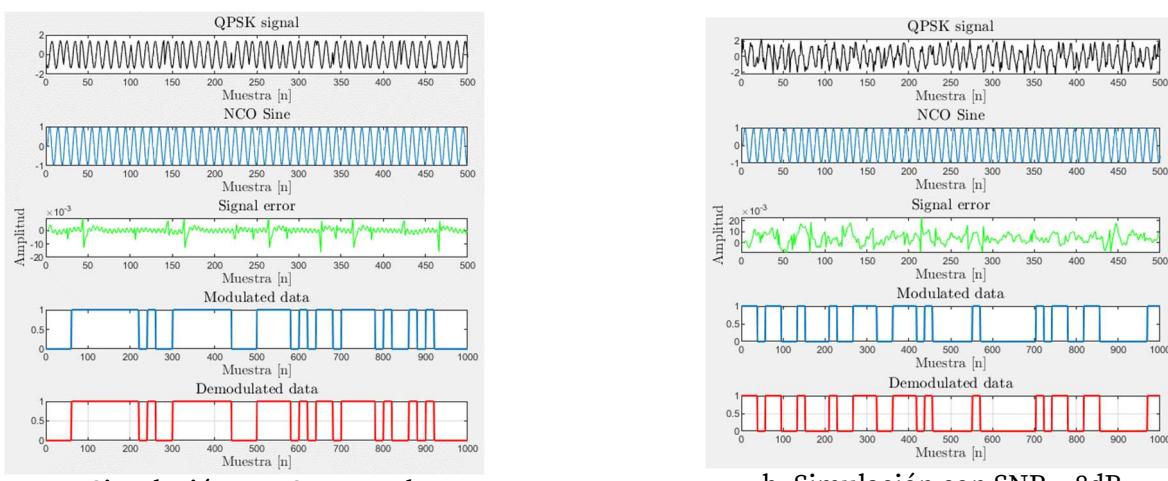

Luego de cargar los parámetros del simulador QPSK, se realizaron dos simulaciones, sin la presencia de ruido y con la presencia de ruido. En la Figura 2a, se muestran los resultados obtenidos con los parámetros descriptos anteriormente, para una SNR de 40dB. En la Figura 2b, se observan los resultados con una SNR de 8dB. En ambas figuras, la primera curva corresponde a la señal QPSK transmitida por el canal de comunicaciones. La segunda curva, corresponde al oscilador local (onda senoidal) generado por el NCO. En la tercera curva, se observa la salida del filtro de lazo, es decir, la señal de error del detector luego de ser filtrada. Por último, las dos últimas curvas muestran los datos modulados y demodulados, respectivamente.

Figura 2: Simulación del demodulador QPSK en un software de simulación matemático

Como se puede observar en la Figura 2a, la señal modulada no tiene ruido, y, por ende, la señal de error del lazo no varía demasiado, lo que quiere decir, que al sistema de lazo cerrado no le cuesta enganchar la fase de la señal. De esta forma, los datos demodulados son idénticos a los modulados.

Por otro lado, en la Figura 2b, se puede ver con claridad que la señal QPSK cuenta con alta presencia de ruido, y la señal de error fluctúa y varía en mayor medida. Sin embargo, el lazo de costas es capaz de recuperar la fase de la señal transmitida, y así, lograr la demodulación de los datos sin mayores inconvenientes.

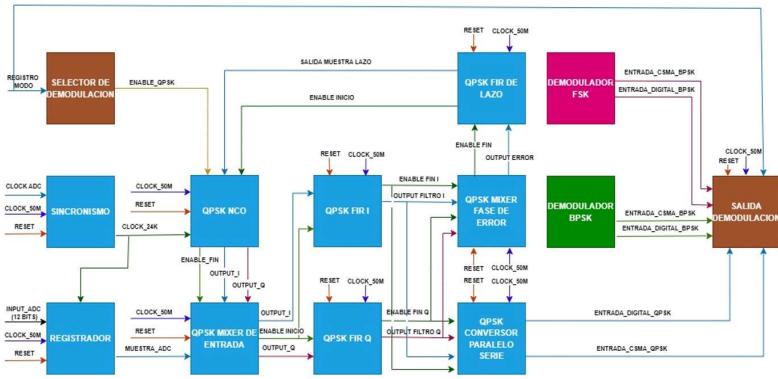

## Diseño del VHDL

Para comprobar el funcionamiento del sistema implementado en hardware, previamente es de gran importancia la simulación del mismo. Para ello, utilizando el software Quartus Prime 18.0, se replicó el simulador de alto nivel anteriormente descripto, pero en este caso, en el lenguaje VHDL. En la figura 3, se muestra el diagrama en bloques del demodulador QPSK.

Figura 3: Diagrama en bloques del lazo de costas en VHDL

A continuación, se describen los bloques fundamentales del demodulador QPSK. Se debe tener en cuenta, que cada bloque del sistema tiene un pulso de habilitación para el siguiente bloque al que está conectado. No se detallarán todos los bloques por cuestiones de espacio y porque son de uso ampliamente difundido.

El bloque de Sincronismo es muy común en circuitos digitales que requieren la sincronización de múltiples relojes (Pong, 2006).

El papel del NCO en el diseño fue explicado anteriormente. Luego de investigar y analizar su funcionamiento, se pudo determinar que su comportamiento es similar al de un DDS (Lupera Morillo & Solano, 2019). Para calcular la frecuencia de salida del NCO, se utilizó la ecuación (7) y se obtuvo que para la frecuencia de portadora a utilizar la fase inicial debe ser 26.

El mixer de entrada, simplemente es el bloque encargado de multiplicar la señal QPSK con los osciladores del NCO.

Se estableció el orden de los filtros FIR en 8. Se utilizaron coeficientes de 18 bits con signo, correspondientes a un filtro pasabajos con frecuencia de corte en 600 Hz. A la salida, se utilizaron dos filtros FIR idénticos, para suavizar la señal y mejorar la detección. La salida de los últimos filtros, no se tiene en cuenta para la detección de error.

Para implementar el detector de error que se aprecia en la Figura 1, se utilizaron 4 condicionales “if” para detectar los signos de cada rama en cada ciclo de reloj, de forma tal, que solo se utiliza una suma en lugar de dos productos.

Para la implementación del filtro de lazo, se calcularon las constantes  $K_L$  y  $K_I$ , utilizando las ecuaciones (5) y (6) con los siguientes parámetros:  $\omega_n = 2\pi \cdot 500 \text{ Hz}$ ,  $\zeta = 0.5$  y  $K_{NCO} = 1$ . Se obtuvieron un  $K_L=5243$  y un  $K_I=57$ . Estos coeficientes, se almacenaron en un arreglo de dos elementos de 18 bits con signo.

El conversor paralelo-serie es la etapa final del demodulador, en la cual, a partir de las dos ramas (I y Q) que salen de los filtros FIR, se obtiene una única salida. Esto se logra, tomando los bits de una rama en un ciclo y los bits de la otra en el ciclo siguiente. Una vez que se unen las ramas, se procede a decidir si el bit que ingresa corresponde a un uno o a un cero.

## Simulación en ModelSim

Para la simulación del sistema, se generó un archivo de pruebas en el cual se configuraron todos los parámetros necesarios para emular el comportamiento visto en la simulación de alto nivel. Además, este archivo contiene la señal de entrada QPSK que excita al demodulador.

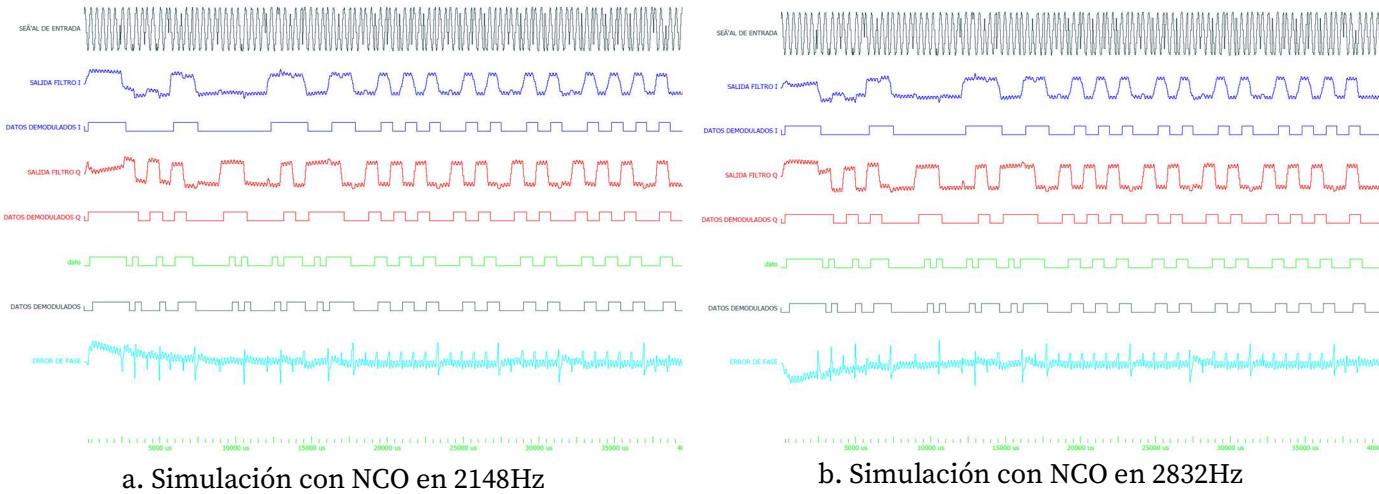

Las simulaciones, tienen como objetivo verificar el comportamiento del sistema con diferentes niveles de SNR en la señal de entrada, para lo cual se agregó ruido gaussiano a dicha señal desde el software matemático. Por otro lado, se quiere determinar cuál es la frecuencia mínima y máxima a la cual puede enganchar el filtro de lazo. Para ello, se varió la fase inicial de NCO, y luego de una serie de pruebas, se determinó que dichas frecuencias, se dan con fase mínima de 22 y 29, que corresponden a frecuencias de 2148Hz y 2832Hz, respectivamente. Esto indica que la señal, puede tener variaciones de  $\pm 342\text{Hz}$ . A continuación, se detallan las simulaciones realizadas.

### Simulaciones con fases del NCO mínima y máxima, con SNR de 40 dB

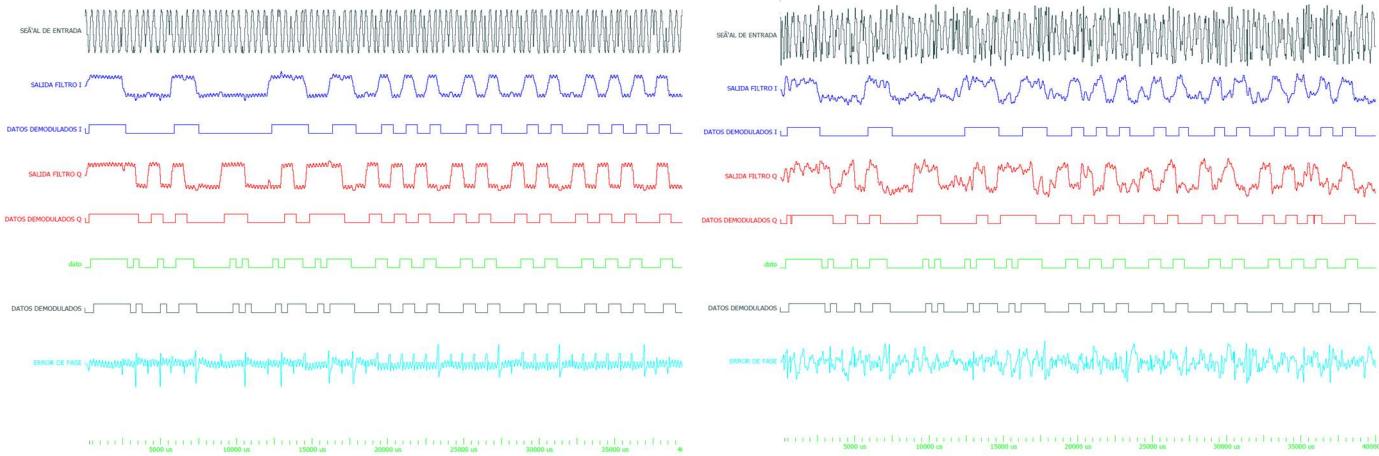

En este caso, en primer lugar, se deja constante el nivel de ruido, pero se utiliza la fase mínima del NCO para que pueda enganchar el filtro de lazo. En la Figura 4a, se pueden observar los resultados de esta simulación. Al igual que en el caso anterior, se realizó otra simulación en la que la SNR se mantuvo en 40 dB, pero el NCO se ajustó con una fase inicial de 29. Los resultados de esta simulación, se pueden observar en la Figura 4b.

Figura 4: Simulación en los límites del NCO con SNR = 40dB

Las curvas negras corresponden a la señal modulada y los datos demodulados, respectivamente. Las curvas azules y rojas corresponden a las entradas y salidas de los filtros FIR de las ramas I y Q, respectivamente. Por otro lado, la señal verde corresponde a los bits transmitidos y la señal cian es el error de fase generado a través del tiempo. Esta disposición de curvas, se mantiene para el resto de simulaciones mostradas en el presente documento.

Observando los resultados de ambas simulaciones, se puede apreciar que, el lazo de costas recupera la fase de la señal modulada en los dos casos. Es decir que, en las dos frecuencias iniciales, el lazo de costas puede enganchar la fase y los datos ser recuperados sin problemas. Para determinar las fases mínima y máxima, se realizaron numerosas simulaciones variando la fase del NCO y se comprobó que el lazo no podía seguir la fase como debe, utilizando fases del NCO menores a 22 y mayores a 29.

### Simulaciones con fase del NCO en 26 y SNR de 40 dB y 8dB

En estas simulaciones, se utilizó una señal de entrada con SNR = 40dB para uno de los casos y una señal con SNR = 8dB para el otro caso, ambas con fase inicial del NCO en 26. En las Figuras 5a y 5b, se pueden observar los resultados de ambas simulaciones.

En la Figura 5a, puede apreciarse con claridad, que el lazo de costas engancha la fase rápidamente, el NCO tiene la misma frecuencia que la portadora y los datos se recuperan correctamente. Por otro lado, en la Figura 5b, pese a que el nivel de ruido en la señal de entrada no es tan elevado, como por ejemplo con una SNR de 5dB, se aprecia que las fluctuaciones en el error de fase que se producen son grandes, pero, aun así, el lazo de costas puede enganchar la fase de la portadora y, por lo tanto, los datos se pueden recuperar con éxito.

a. Simulación con SNR = 40dB

b. Simulación con SNR = 8dB

Figura 5: Simulaciones con NCO en 2343 Hz

## Conclusiones

En base a las simulaciones realizadas, se puede concluir que el demodulador QPSK, funciona de forma correcta y presenta un aceptable alcance de ruido. Una ventaja, es el rango máximo de enganche a frecuencia inferiores y superiores en relación al posicionamiento inicial del NCO.

Un aspecto importante del demodulador QPSK, es la relación de velocidad de transmisión y ancho de banda, teniendo en cuenta que el objetivo radica en la transmisión de información en un ancho de banda de 3kHz, y el mismo no puede variar. Por ejemplo, la modulación QPSK permite enviar el doble de información que BPSK, manteniendo su ancho de banda, o bien, enviar la misma información que BPSK, disminuyendo el ancho de banda a la mitad, por lo que resulta muy provechosa su utilización en este tipo de aplicaciones.

Se comprobó, que el sistema no tiene una muy buena inmunidad al ruido ya que el valor mínimo de SNR sin cometer errores de detección es de 8dB, lo que es contraproducente para trabajar en canales de HF, que suelen ser problemáticos en los sistemas de comunicaciones.

## Referencias

- Campbell, R. F. (2016). *Analysis of Various Algorithmic approaches to Software-Based 1200 Baud*.

- Ghaffari, M., Hosseini, E., & Sadr, A. (2016). Design of a resource efficient BPSK demodulator based on. *2nd International Conference on Information, Technology, Communications and Telecommunications (irlCT)*. Teheran.

- Howard, R. M. (2015). White noise: a time domain basis. *International Conference on Noise and Fluctuations (ICNF)*. Xi'an China.

- Lupera Morillo, P. A., & Solano, N. (2019). Diseño e implementación de un demodulador QPSK utilizando una técnica de tendencia central. *MASKAY*, 9(2), 51-57. doi:<https://doi.org/10.24133/maskay.v9i2.1170>

- Osborne, H. (OCTOBER 1982). A generalized "polarity-type" costas loop for tracking MPSK signals. *Communications, IEEE Transactions on*, 30(10), 2289-2296.

- Pong, P. C. (2006). *RTL hardware design using VHDL*. Hoboken, New Jersey: John Wiley and sons, Inc.

- Staszewski, R. B., & Balsara, P. T. (MARCH 2005). Phase-Domain All-Digital Phase-Locked Loop. *IEEE Transactions on Circuits and Systems II: Express Briefs*, 52(3), 8.

- Tomasi, W. (2003). *SISTEMAS DE COMUNICACIONES ELECTRONICAS* (4 ed.). Pearson.